LatticeECP3 Delivers Rock Solid SERDES for Low Cost PCIe 2.0 Designs

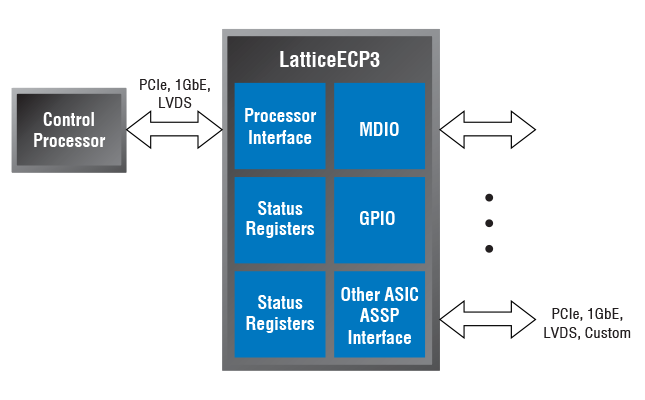

The LatticeECP3 PCIe Solution is the first and only PCI Express 2.0 compliant low cost FPGA. With rock solid SERDES, an advanced PCI Express IP Core and a full-featured development kit the LatticeECP3 solution is ready to accelerate your next PCIe innovation, with an affordable price tag.

- With up to 16 channels of low cost, low power SERDES, DSP slices, high-speed DDR3 memory interface capability and efficient FPGA fabric, the LatticeECP3 has all the features required for PCIe applications.

- The Lattice PCI Express Endpoint IP Core has the advanced features needed to easily integrate PCIe 2.0 functionality with your design. Additionally, the Lattice Scatter Gather DMA IP Core can be used to further optimize transfer bandwidth.

- The LatticeECP3 Versa Development Kit includes the full-featured evaluation board (with LatticeECP3 FPGA, Flash and DDR3 memory), free Lattice Diamond design environment, reference designs, demonstration systems and complete user documentation.

Visit the “LatticeECP3 PCIe Information Page” to learn how to simplify your low cost PCIe applications, or please contact Allyanz today for more details.

Lowest Power SERDES-capable FPGA in the industry

The LatticeECP3 family is the third generation high value FPGA from Lattice Semiconductor, which offers the industry’s lowest power consumption and price of any SERDES-capable FPGA device. The LatticeECP3 FPGA family offers multi-protocol 3.2G SERDES with XAUI jitter compliance, DDR3 memory interfaces, powerful DSP capabilities, high density on-chip memory and up to 149K LUTS, all with half the power consumption and half the price of competitive SERDES-capable FPGAs.

Features include:

- Low-power 65nm process with 4-input look-up table (LUT) fabric

- Logic densities from 17K to 149K LUTs

- Upto 6.8Mbits of Embedded Block RAM (EBR)

- 2 DLLs per device, 2 to 10 PLLs per device

- High Speed embedded SERDES

- Multiply, accumulate, addition and subtraction

- High performance Adder Trees and MMAC functionality

- 54-bit Cascadable Arithmetic Logic Unit

- 24 to 320 multipliers (18×18)

- Advanced configuration options

- Flexible I/O buffers

- Wide range of Package & User I/O options

For more information on the LatticeECP3 family of FPGAs, or development tools to support your design requirements, please contact us.