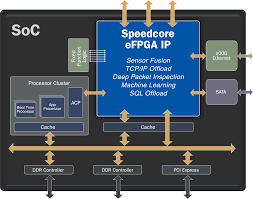

Achronix Speedcore embedded FPGA (eFPGA) IP from Achronix has brought the power and flexibility of programmable logic to ASICs and SoCs.

Customers can integrate a Achronix Speedcore eFPGA into an SoC for high-performance, compute-intensive and real-time processing applications such as AI, machine learning, 5G wireless, networking and automotive.

Proven on the TSMC 16FF+ process node, Speedcore eFPGA IP enables customers to create a customized programmable fabric.

Users specify their logic, memory and DSP resource needs, then Achronix configures the Speedcore IP to meet their individual requirements. Speedcore look-up-tables (LUTs), RAM blocks and DSP64 blocks can be assembled like building blocks to create the optimal programmable fabric for any given application. Achronix delivers the customized Speedcore eFPGA instance as a hard macro in GDSII format along with a customized version of ACE design tools.

There are many benefits to embedding Speedcore technology into an SoC. Compared to a separate standalone FPGA, Speedcore eFPGA IP offers the following:

- 10× higher bandwidth

- 100× lower latency

- 10× lower cost

- 50% lower power

Achronix Speedcore FPGA Compiled Architecture

As opposed to a one-size-fits-all approach to building an embeddable FPGA fabric, the Speedcore solution is compiled architecture.

Rather than having to pick from a library of pre-built fabrics, a system architect can define a mix of LUTs, LRAMs, BRAMs and DSP blocks for a cluster, then specify overall resource goals for the fabric along with an aspect ratio (expressed in clusters). The resulting fabric is an X by Y array of these custom clusters.

During this specification phase, Achronix returns a detailed proposal on the custom fabric, plus a software model for evaluation using ACE design tools.

Customers can specify the resource counts for their Speedcore instance for the following building blocks:

- Logic – look-up-tables (LUTs) plus integrated wide MUX functions and fast adders

- Logic RAM – 4 kb per memory block

- Block RAM – 20 kb per memory block

- DSP64 – each block has a 18 × 27 multiplier, 64-bit accumulator and 27-bit pre-adder

- Custom blocks – customer/application-specific functions

Resource & performance specifications include:

Speedcore logic density – from 5K to 2M LUTs

Speedcore performance – max 750 MHz

Speedcore power – 12 mW static power per 1,000 LUTs at 105°C (on the TSMC 16FF+ process)

Speedcore die size – 0.20 mm2 per 1,000 LUTs (on the TSMC 16FF+ process)

For more information on SpeedCore eFPGAs from Achronix, please contact Allyanz today.