Single Chip, Non-Volatile LatticeXP2 FPGA

Lattice Semiconductor is now shipping industrial temperature, and automotive temperature (AEC-Q100, with PPAP support) qualified versions of its non-volatile LatticeXP2(TM) FPGAs in volume production quantities. Based on Lattice’s 90 nanometer hybrid flexiFLASH(TM) technology, the XP2 family’s volume production availability enables realization of design requirements in a multitude of industrial applications such as medical imaging, robotics, human machine interface (HMI) systems, motor control and industrial displays, as well as in the tightest form-factor automotive applications such as automotive camera modules, telematics systems, parking assistance systems and multimedia systems.

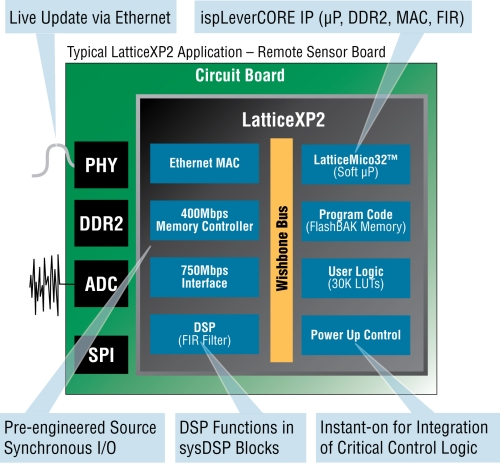

The non-volatile LatticeXP2 FPGA family is a compelling solution for designers who value single chip integration, impressive processing power in the smallest footprint, source synchronous interfaces, design security and low power consumption. The XP2 FPGAs unique benefits include low cost, small form factor Chip Scale 132 BGA packaging, and increased functionality such as embedded sysDSP(TM) blocks, pre-engineered source-synchronous I/O that supports 7:1 LVDS, DDR2 and high-speed ADCs/DACs.

Unlike traditional SRAM-based FPGAs, the LatticeXP2 device does not require an external boot memory for FPGA configuration, which enables a single-chip solution with the associated benefits of reduced board area and simplified system manufacture. The absence of an external boot device also eliminates the need for an external bit-stream at boot up and the possibility of bit-stream snooping, a major security concern with SRAM FPGAs. Additional security features prohibit bit-stream readback from the SRAM and Flash sections of the devices.

The LatticeXP2 design solution offers a unique set of features with broad appeal to a variety of markets, such as video security/ surveillance, LCD/display controllers, automotive systems, medical imaging, and industrial control systems, where processing power must be delivered with high integration in low-cost, small footprint packaging.

About flexiFLASH Architecture

Flash memory blocks are embedded within XP2 FPGAs to store the device configuration, providing a true single chip solution. At power up or on user command, the data stored in the Flash memory is transferred into SRAM cells that control the configuration of the device. This transfer is done in a massively parallel fashion, enabling the device logic to be available in under 1mS, well ahead of the other devices in the system and much faster than SRAM-based FPGAs that use external boot PROMs, regardless of whether they are provisioned separately on-board or stacked in the same package. This instant-on capability is critical for many system functions such as power up sequencing, address decoding and reset logic.

For more details on the single chip, non-volatile LatticeXP2(TM) FPGAs, or development tools to support your design requirements, please contact us.