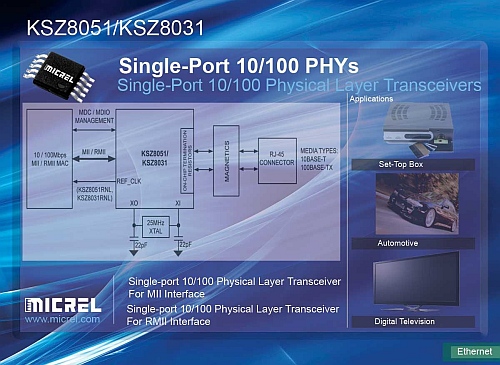

MICREL Cuts Power Requirement For Ethernet Connectivity in Half

Micrel Inc., an industry leader in analog, high bandwidth communications and Ethernet IC solutions, has released the KSZ8051/8031 family of ultra low-power, small package single-port 10/100 Physical Layer Transceivers. These devices provide the MII or RMII interface to transmit and receive data over standard CAT-5 unshielded twisted pair (UTP) cable or fiber. The solution is based on Micrel’s enhanced mixed-signal design which enables power consumption to be reduced by half compared to the prior generation. The devices feature high integration (on-chip termination and integrated regulator), reduced system cost and simplified system design. The ICs also feature higher performance and an extended feature set all in very compact package options.

Full compliance to the IEEE 802.3/802.3u standard ensures that the devices will work seamlessly with other standards compliant, already deployed devices. The ultra low power design satisfies the green requirement in today’s consumer, industrial and automotive Ethernet applications. On-chip termination not only eliminates components, simplifies PCB design and reduces system BOM, but also improves overall signal integrity and EMI emissions. The single external power supply (3.3V), with integrated regulator, enables core operation at 1.2V with IO at 1.8V/2.5V/3.3V. The KSZ8051MLL/FLL comes in a 48-pin LQFP package and provides a MII MAC interface with the option to interface to copper or fiber media. The KSZ8051MNL/RNL is a copper transceiver housed in a 32-pin QFN with the option for a MII or RMII MAC interface. The KSZ8031RNL offers the smallest package, 24-pin QFN, with an RMII MAC interface. Auto MDI/MDIX crossover support eliminates the need for a cross-over cable, thus reducing installation costs. Easy to use, the LinkMD(R) TDR-based cable diagnostics allow for identification of common cabling problems, including those not addressed by IEEE standards. This simplifies network deployment and reduces network downtime.

The low emissions and Micrel’s signature high reliability and quality also make these devices suitable for connectivity applications in the fast growing industrial automation and automotive markets.

For more details on these new PHY Layer Transcievers from Micrel, please contact us.

Lattice FPGA Design Software Webinar Australia / New Zealand – September 8, 2010

Lattice Power 2 You! Webinar Series –

Australia / New Zealand – September 8, 2010

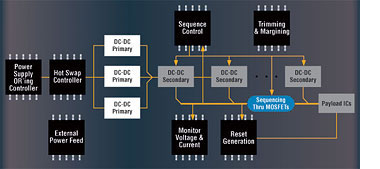

The Power 2 You! webinar helps you understand key design criteria for the power management functions shown in the below figure. In addition, the webinar will show you how to integrate them into a Power Manager II device. The resulting solution can be used across a wide range of applications and can be individually customized using Lattice’s PAC-Designer (R) software.

Attend this FREE Lattice Semiconductor seminar and you will walk away with in-depth technical knowledge of Lattice’s Power Manager Solutions.

All attendees receive a free copy of the Power 2 You! reference manual.

Learn How to Design

- Hot swap controllers

- Supply OR’ing controllers using MOSFETs

- Power feed through MOSFETs

- Power supply sequencing with and without MOSFETs

- Reliable monitoring voltages for fault and reset generation

- Trimming and margining of board-mounted supplies

For more information please contact us.

WIMA RFI Capacitors with High Corona Inception Voltag

The MKP-X2 R series capacitors from WIMA are suited to demanding AC voltage circuits e.g. where voltage is supplied via a capacitor power supply (the capacitor is switched in series to the load circuit as a low-loss series impedance). Due to their internal series connection the capacitors exhibit about twice as high corona inception voltage, resulting in higher rated AC voltage values than comparable components without this series connection.

WIMA MKP-X2 R capacitors are available with extended capacitance values up to 10  F and a rated voltage of 400 VAC.

F and a rated voltage of 400 VAC.

For more details on the MKP-X2 R series of RFI capacitors from WIMA, please contact us.

Lattice Releases Development Platform for SERDES and Video Clock Distribution

Lattice Semiconductor is now shipping its US$169 evaluation board for the ispClockTM 5400D programmable clock device.

The new board is an easy-to-use platform for evaluating and designing with the ispClock5400D differential clock distribution device. The evaluation board can be used by itself to review the performance and in-system programmability of the 5400D device, or as a companion board and clock source for LatticeECP3TM FPGA Serial Protocol or Video Protocol evaluation boards.

Typically, expensive oscillators with LVDS or LVPECL interfaces are used as a reference clock for FPGA SERDES interface applications. The ispClock5400D device provides ultra low-jitter differential clock outputs that can be used to drive both the general purpose clocks and the SERDES reference clocks for FPGAs, ASSPs and ASICs. The evaluation board demonstrates how to interface a low-cost CMOS interface oscillator to the ispClock5400D device to produce high quality clocks for XAUI applications or 270 MHz SDI video applications.

About ispClock Programmable Clock Devices

The ispClock5400D device family features in-system programmable differential clock distribution with fully programmable features that allow users to program in different frequencies based on dividers and PLL functions. Additional value is added with multiple differential I/O support for various standards while maintaining the low-jitter required for high performance systems. The ispClock5400D family supports differential output drivers for programmable differential input reference/feedback standards: LVDS, LVPECL, HSTL, SSTL and HCSL. Included on-chip are programmable termination and a clock A/B selection multiplexer, programmable time skew, programmable phase skew and various programmable output enable features. Through I2C the user has access to nearly all the programmable features of the ispClock5400D.

The ispClock5400D maintains extremely low-jitter:

- Ultra low cycle-to-cycle jitter (29ps p-p)

- Ultra low period jitter (2.5ps)

- Low output-to-output skew (<75ps)

About LatticeECP3 FPGAs

The low power, high value, third generation LatticeECP3 family offers the industry’s lowest power consumption and price of any SERDES-capable FPGA devices.The LatticeECP3 FPGA family offers multi-protocol 3.2G SERDES with XAUI jitter compliance, DDR3 memory interfaces, powerful DSP capabilities, high density on-chip memory and up to 149K LUTS, all with half the power consumption and half the price of competitive SERDES-capable FPGAs.

For more details on the low cost Evaluation board, ispClock5400D devices or ECP3 SERDES-capable FPGAs, please contact us.

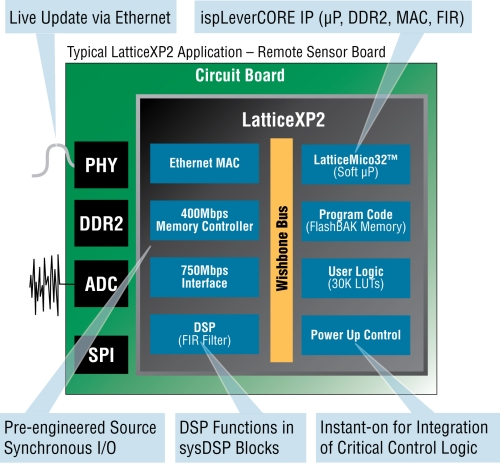

Single Chip, Non-Volatile LatticeXP2 FPGA

Lattice Semiconductor is now shipping industrial temperature, and automotive temperature (AEC-Q100, with PPAP support) qualified versions of its non-volatile LatticeXP2(TM) FPGAs in volume production quantities. Based on Lattice’s 90 nanometer hybrid flexiFLASH(TM) technology, the XP2 family’s volume production availability enables realization of design requirements in a multitude of industrial applications such as medical imaging, robotics, human machine interface (HMI) systems, motor control and industrial displays, as well as in the tightest form-factor automotive applications such as automotive camera modules, telematics systems, parking assistance systems and multimedia systems.

The non-volatile LatticeXP2 FPGA family is a compelling solution for designers who value single chip integration, impressive processing power in the smallest footprint, source synchronous interfaces, design security and low power consumption. The XP2 FPGAs unique benefits include low cost, small form factor Chip Scale 132 BGA packaging, and increased functionality such as embedded sysDSP(TM) blocks, pre-engineered source-synchronous I/O that supports 7:1 LVDS, DDR2 and high-speed ADCs/DACs.

Unlike traditional SRAM-based FPGAs, the LatticeXP2 device does not require an external boot memory for FPGA configuration, which enables a single-chip solution with the associated benefits of reduced board area and simplified system manufacture. The absence of an external boot device also eliminates the need for an external bit-stream at boot up and the possibility of bit-stream snooping, a major security concern with SRAM FPGAs. Additional security features prohibit bit-stream readback from the SRAM and Flash sections of the devices.

The LatticeXP2 design solution offers a unique set of features with broad appeal to a variety of markets, such as video security/ surveillance, LCD/display controllers, automotive systems, medical imaging, and industrial control systems, where processing power must be delivered with high integration in low-cost, small footprint packaging.

About flexiFLASH Architecture

Flash memory blocks are embedded within XP2 FPGAs to store the device configuration, providing a true single chip solution. At power up or on user command, the data stored in the Flash memory is transferred into SRAM cells that control the configuration of the device. This transfer is done in a massively parallel fashion, enabling the device logic to be available in under 1mS, well ahead of the other devices in the system and much faster than SRAM-based FPGAs that use external boot PROMs, regardless of whether they are provisioned separately on-board or stacked in the same package. This instant-on capability is critical for many system functions such as power up sequencing, address decoding and reset logic.

For more details on the single chip, non-volatile LatticeXP2(TM) FPGAs, or development tools to support your design requirements, please contact us.